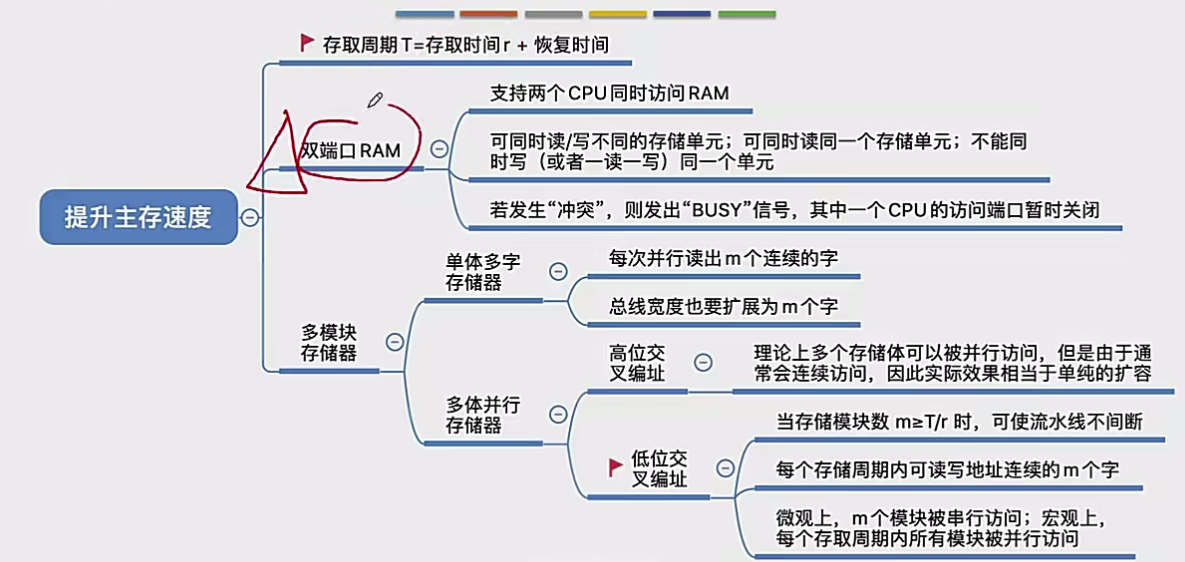

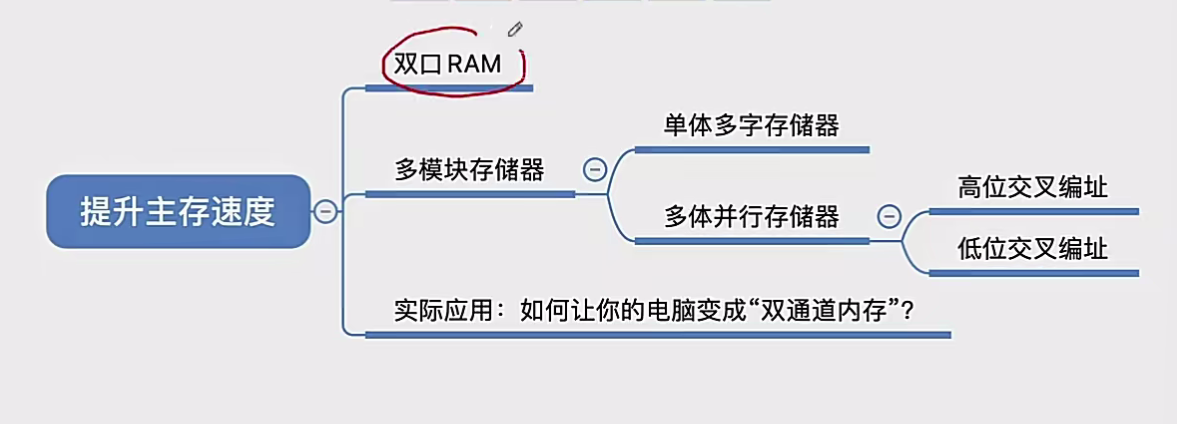

¶双端口ROM

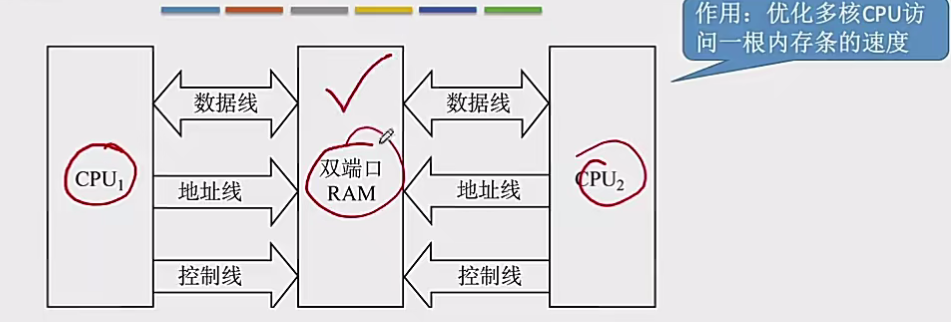

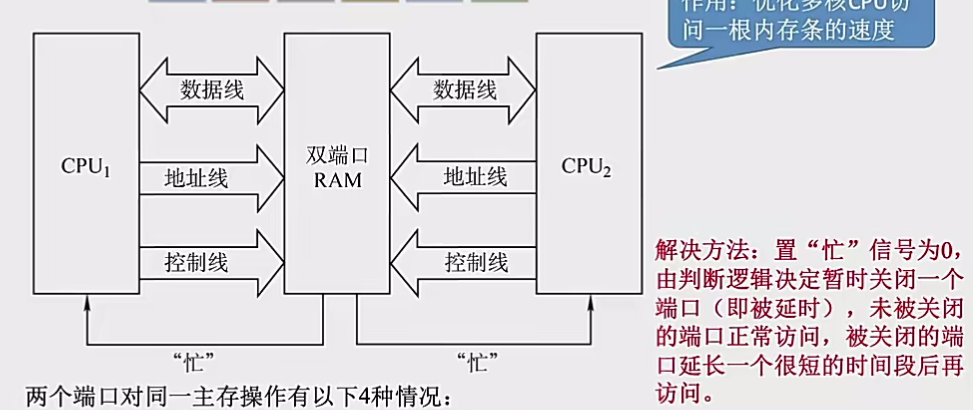

需要由两组完全独立的数据线、地址线、控制线。

CPU、RAM中也要有更复杂的控制电路

两个端口对同一主存操作有一下4种情况

-

两个端口同时对不同的地址单元存取数据。👌

-

两个端口同时对同一地址单元读出数据👌

-

两个端口同时对同一地址单元写入数据🚫

-

两个端口同时对同一个地址单元,一个写入数据,一个读出数据🚫

对比操作系统,”读者写者问题”

¶多体并行存储器

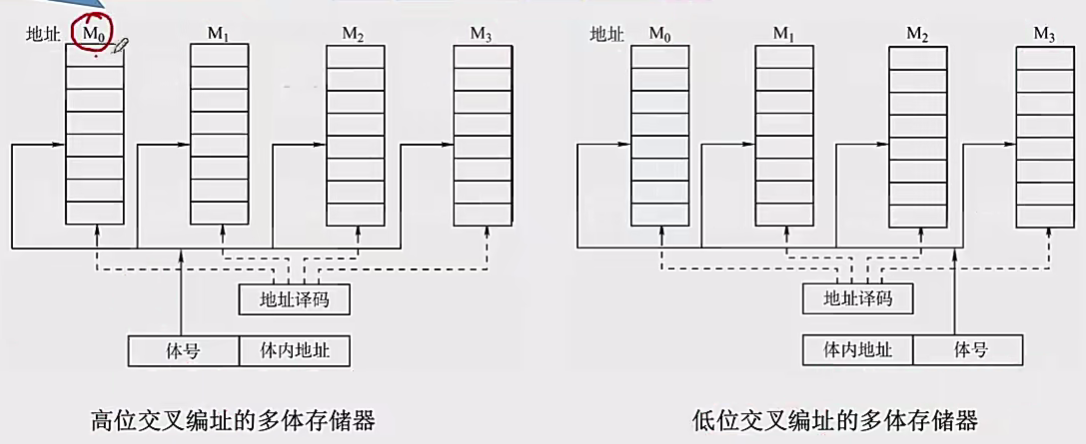

¶交叉编址

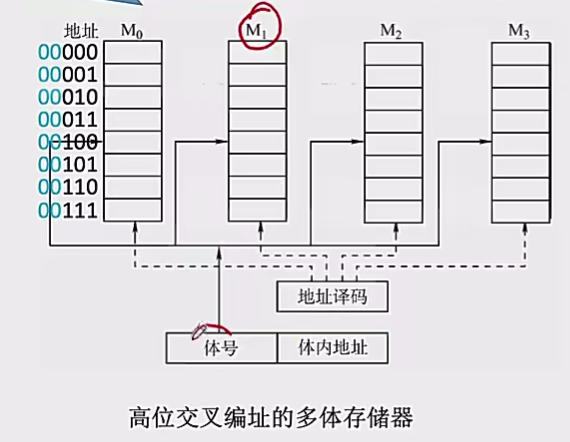

¶高位交叉编址

地址的前几位表示是哪一个芯片

如 , 上图中 , 高位部分 (前面的00) 就是用于表示选择$M_0$芯片的

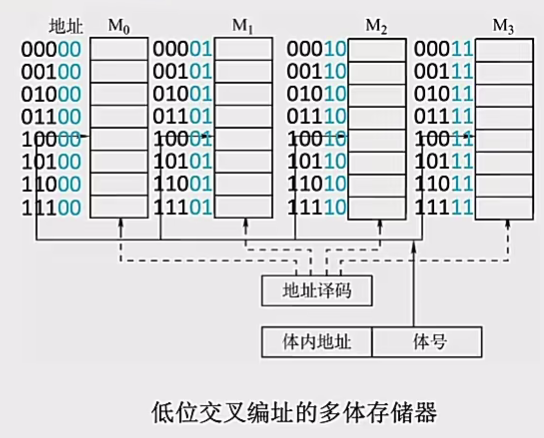

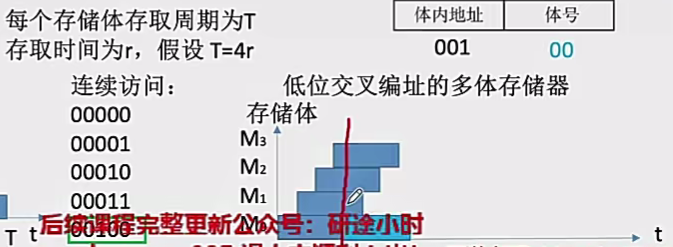

¶低位交叉编址

对于高位交叉编址, 和低位交叉编址.

地址的实际值是不太一样的

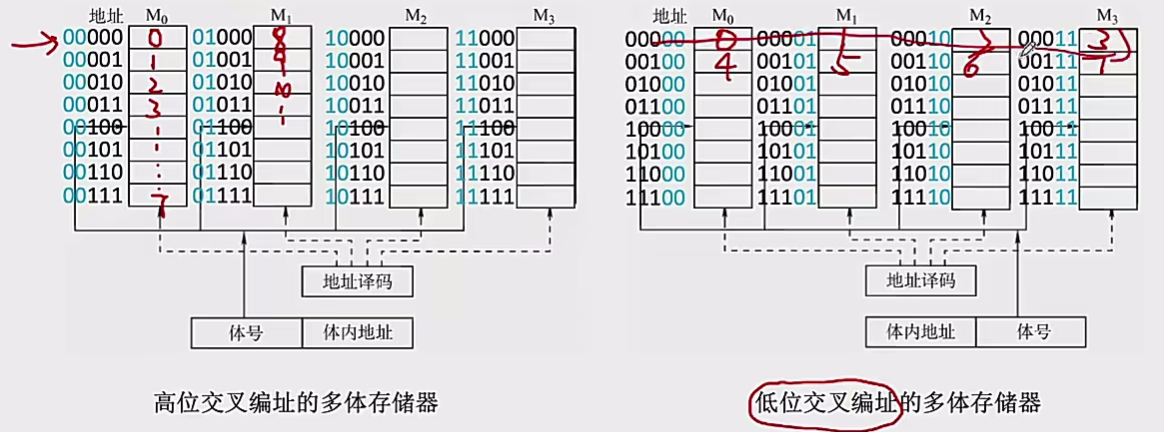

对于高位交叉编址, 就像是在第一个内存条编完0~7

在到下一个内存条边8之后的

而, 地位交叉编址, 就像是横着编址

先从第一个存储器到最后一个存储器, 依次在第一个存储单元上编上0~4

在从第一个存储器第二个存储单元开始,依次往后编址

在交叉编址的多体存储器部分

连续访问同一个存储体, 是需要等待刷新时间的

即, 需要等待一个整个存取时间(加上了刷新时间)

当需要读出地址连续的四个单元时, 低位交叉编址和高位交叉编址访存时间不同

-

对高位交叉编址, 访问连续地址时, 由于高位不变, 实际上是访问同一块存储体的连续地址, 则每次读取都需要等待一整个存取周期

-

对于低位交叉编址, 访问连续地址时, 由于低位是变化的, 实际上是在分别访问每块存储体的相同位置的存储单元, 而访存完第一个存储体, 无需等待第一个存储体是否完成刷新, 直接访问第二个就可以

若, 设每个存储体存取周期为$T$

存取时间为$r$, 假设$T=4r$

则, 访问高地址交叉编址需要耗时$5T$, 访问低地址交叉编址需要耗时$T+4r$

低位交叉编址的多体存储器,连续取n个存储字耗时$T+(n-1)r$

宏观上来看,读写一个字的时间接近$r$

因为,在实际使用中,程序寻访的通常是连续的地址空间

所以这里讨论的就是连续访问连续地址的情况

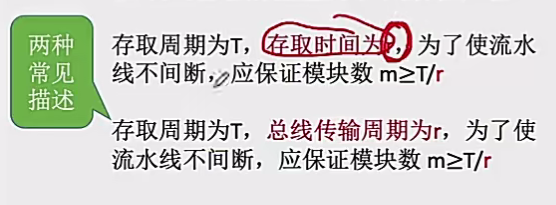

¶应该取几个“体”

采用流水线的方式并行存取(宏观上并行,微观上串行)

宏观上,一个存储周期内,m体交叉存储器可以提供的数据量位单个模块m倍

存取周期为T,存取时间为$r$

为了使流水线不间断,应保证模块数 m>=T/r

如何判断当前读取的是那个存储体?

首先可以将地址转为2进制,然后看最后几个

或者,将地址对单元数取余

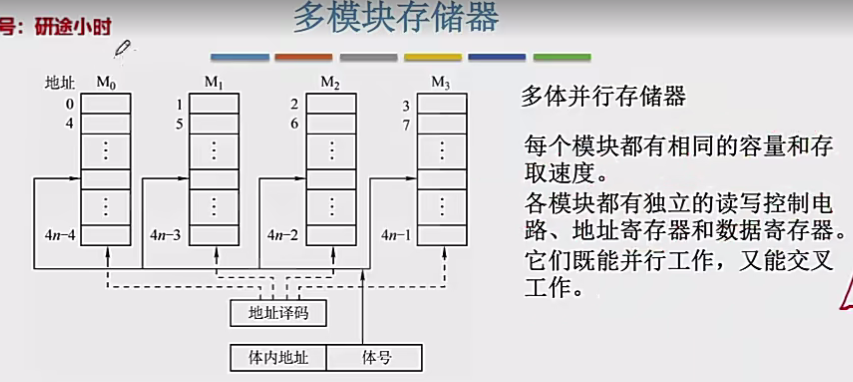

¶多模块存储器

¶多体并行存储器

每个模块都有相同的容量和存取速度。

各模块都有独立的读写控制电路、地址寄存器和数据寄存器。

他们既能并行工作,又能交叉工作

¶单体多字存储器

每个存储单元存储$m$个字

总线宽度为$m$个字

一次并行读出$m$个字

每次只能同时取$m$个字,不能单独存取其中某个字

指令和数据在主存内必须是连续存放的