相关链接|改错

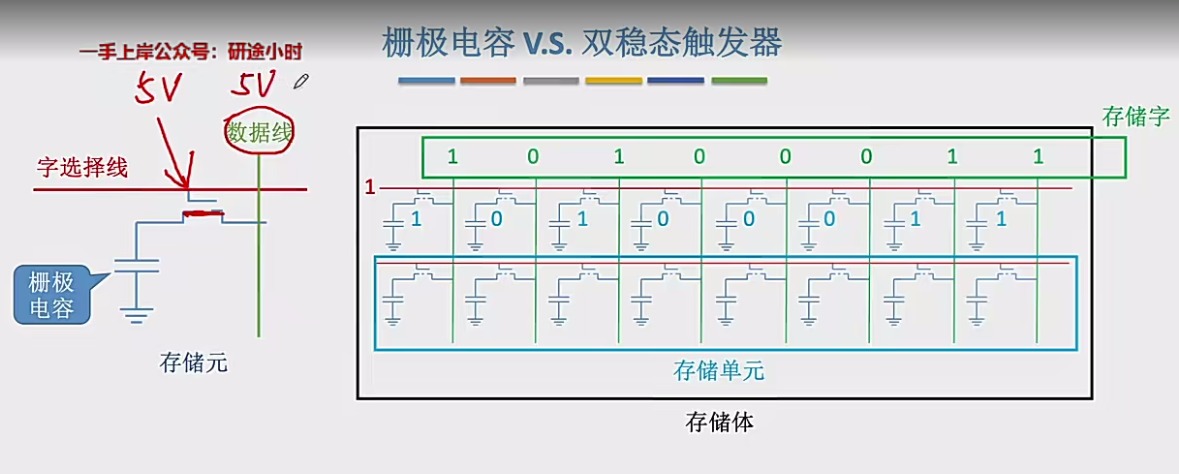

¶栅极电容与双稳态触发器对比

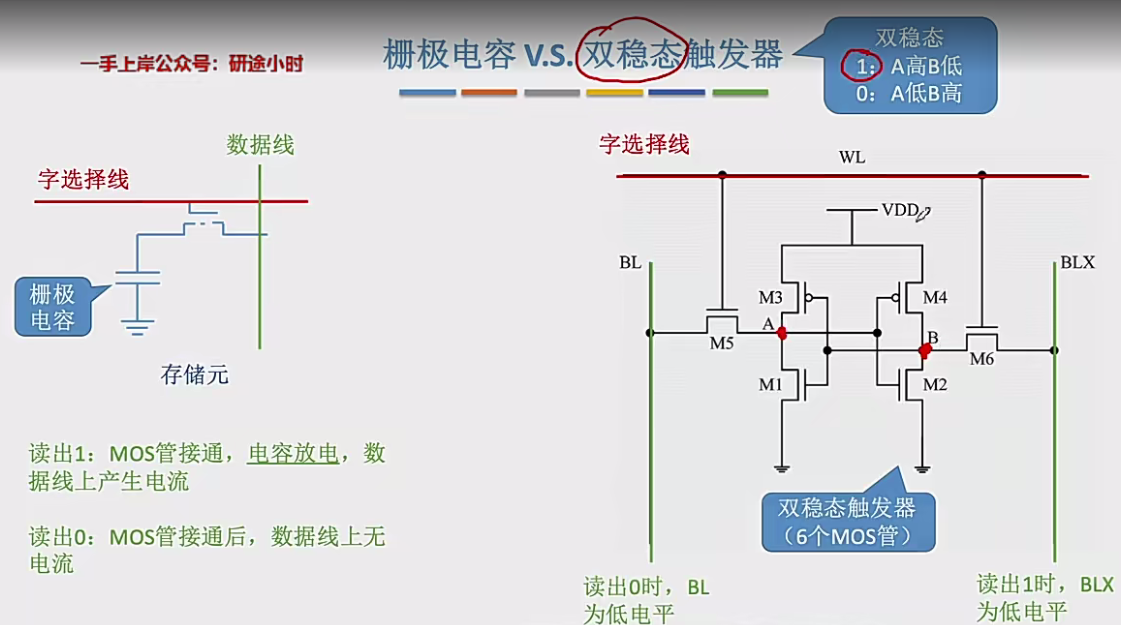

¶栅极电容

-

读出1:MOS管接通,电容放电,数据上产生电流

电容放电信息被破坏,是破坏性读出。读出后应有重写操作,也称再生

另外,电容内的电荷只能维持2ms,即使不断电,2ms后信息也会消失,2ms之内必须“刷新”一次(给电容器充电)

-

读出0:MOS管接通后,数据线上无电流

每个存储器制造成本更低,集成度高,功耗低

¶双稳态触发器

-

读出0:BL为低电平

-

读出1:BLX为低电平

读出数据,触发器状态保持稳定,是非破坏性读出,无需重写

每个存储元制造成本更高,集成度低,功耗大

¶DRAM的刷新

-

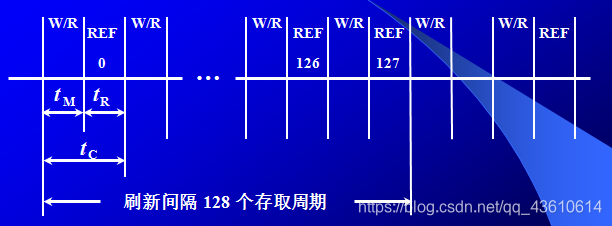

多久需要刷新一次:刷新周期,一般为2ms

-

每次刷新多少存储单元:以行为单位,每次刷新一行存储单元

-

如何刷新:

有硬件支持,读出一行的信息后重新写入,占用1个 读/写周期

TIP该处说明,无论哪种刷新方式,DRAM的刷新方式均是以行刷新的模式刷新的

-

在什么时候刷新:

-

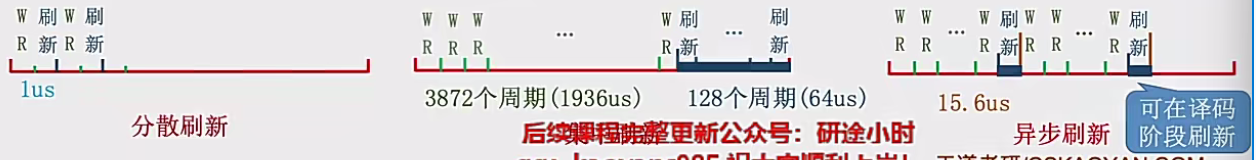

思路一:每次读写完就刷新一次

-

系统的存取周期变为1us

前0.5us用于正常读写

后0.5us用于刷新某行

-

-

思路二:2ms内集中全部刷新

-

系统的存取周期还是0.4us

有一段时间专门用于刷新

无法访问存储器,称为访存"死区"

-

-

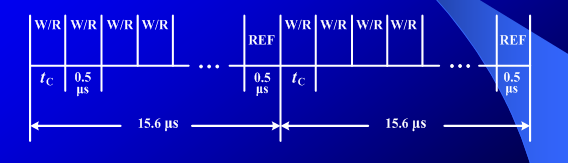

思路三:2ms内每行刷新1次即可

-

2ms/128 = 15.6us一次

每15.6us内有0.5us的"死时间"

-

-

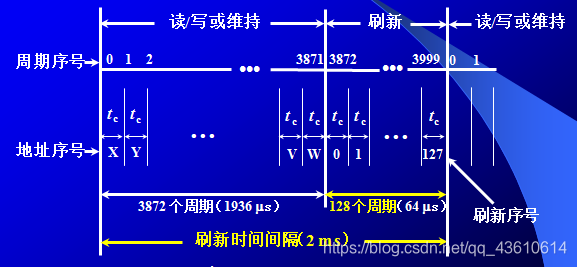

集中刷新:

在规定的一个刷新周期内,对全部存储单元集中一段时间逐行进行刷新(用专门的时间进行刷新)

例

对128*128的存储芯片进行刷新,存储周期为0.5$\mu s$ ,刷新周期为2ms(再刷新到这里)

刷新:是对信息读出再写入,所以所需要的时间也是0.5$\mu s$

2ms的刷新周期,所占存取周期数为,$2000 \mu s/0.5\mu s = 4000\text{(个)}$

共有128行需要进行刷新,则刷新占128个存取周期,则刷新时间为:

$128 * 0.5\mu s = 64 \mu s$

读/写或维持的时间:

$2000\mu s-64\mu s = 1936\mu s$

读/写或维持的存储周期为

4000-128 = 3872(个)

-

分散刷新

是指对每行存储单元的刷新分散到每个存储周期内完成(对某一行某芯片进行读写操作后,紧接着刷新 包含在了读写周期内)

例:对128×128的矩阵的存储芯片进行刷新,读/写周期为0.5s(读一次或写一次),

将刷新分散到存储周期内完成,则存储周期就包含了刷新时间

此时,存储周期(存储器进行两次独立的存储器操作 读或写)为

$t = 0.5\mu s + 0.5 \mu s= 1\mu s$

刷新(刷新以行算)一行的时间为$1\mu s$,全部刷新完的时间为:

$128 * 1\mu s = 128\mu s$

此时比2ms小的多,在刷新到此间隔$128\mu s$

-

优点:无死区

-

缺点:存取周期长,整个系统的速度降低了

-

-

异步刷新

前两种方式的结合,缩短了死时间,充分利用了最大刷新间隔为2ms的特点(只要在2ms内对这一行刷新一遍就行)

例:对128×128的矩阵的存储芯片进行刷新,存储周期为0.5s,刷新周期为2ms

刷新周期:即一个单元最长过多长时间必须刷新一次

2ms对每行刷新一遍

$2000\mu s /128 = 15.6\mu s$

即每隔15.6μs刷新一行

每行的刷新时间仍然为0.5μs。刷新一行就停一个存储周期,“死时间缩短为0.5μs”(15.6μs内刷新一行 其他全用来读写)

-

“刷新”由存储器独立完成,不需要cpu控制

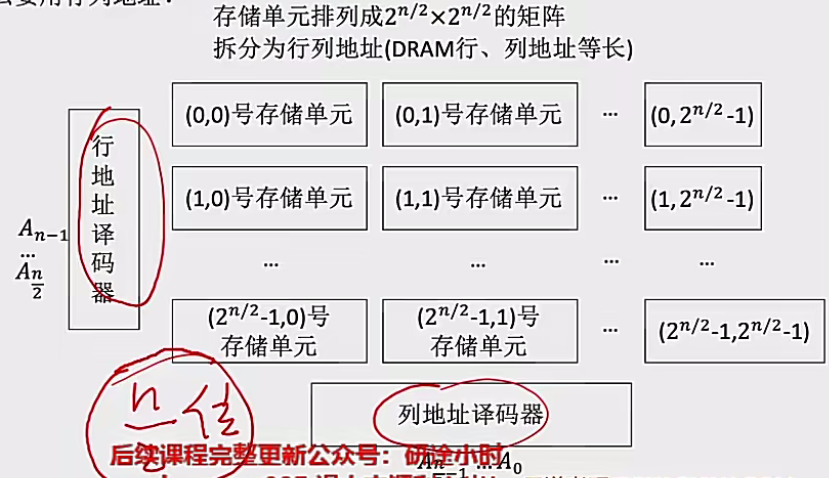

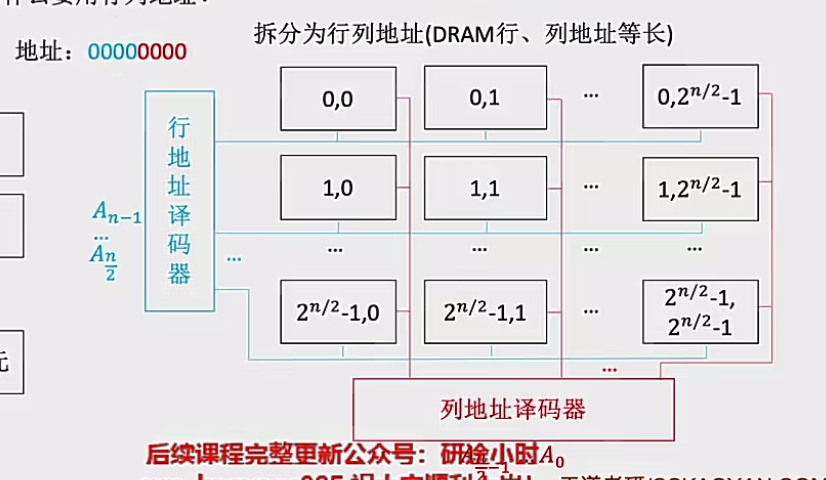

DRAM通常使用行列地址,以减少选通线的数量

因为如果只用一维地址线,大容量存储就会使用非常多的地址线

所以在实际使用时,一般采用二维地址线,即行列地址线

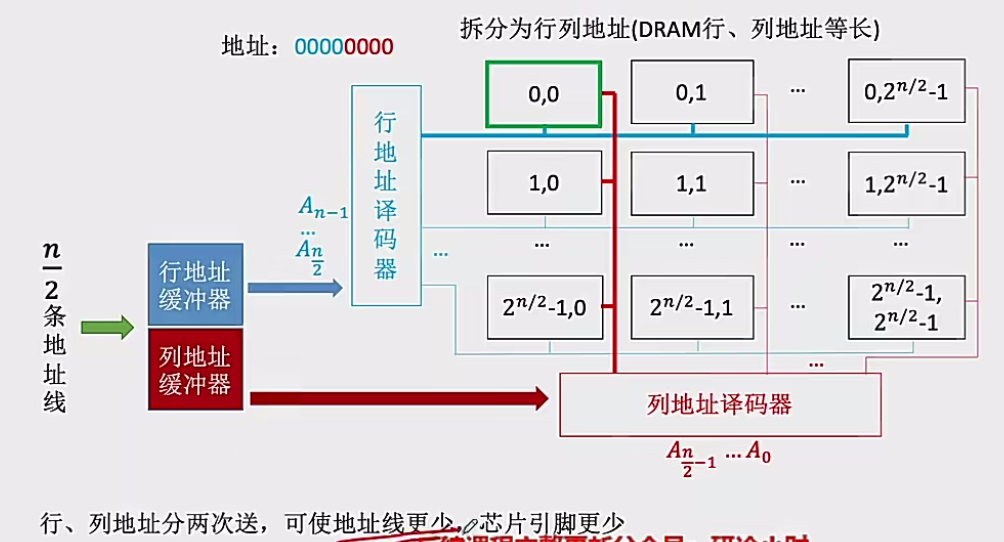

¶DRAM地址线时分复用技术

因为DRAM需要很长的寻址,所以将行地址与列地址进行复用

则只需要$\frac{n}{2}$条地址线

在地址解析时,

先将行地址通过地址线放入行地址缓冲器

再将列地址通过地址线放入列地址缓冲区

地址线复用技术,导致地址线、地址引脚减半

现在的主存通常采用SDRAM芯片

SDRAM:同步动态刷新存储器,是现在最常用的一种DRAM